검색결과 리스트

Learning stuff에 해당되는 글 56건

- 2012.09.11 mosfet 기호

- 2012.08.08 엑셀로 피팅

- 2012.08.03 SBD

- 2012.08.03 오프컬렉터

- 2012.07.27 labview

- 2012.07.27 matlab interp 2

- 2012.04.12 Converters

- 2012.04.11 OP AMP의 기본동작 1

- 2012.04.11 Open collector, Open drain

- 2012.04.11 schmitt trigger

글

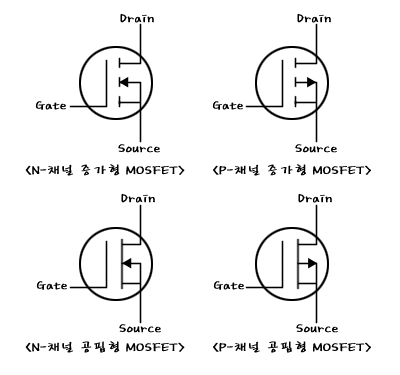

mosfet 기호

부끄럽지만 이거 나 매일 헷깔려....

기호 말이야 기호ㅋㅋㅋ

N 형이 들어오는거고 P형이 나가는거야 그래

화살표는 N 형이면 전자 P 형이면 정공 이라고 보면 된다 즉

N형이면 +걸때 Drain 에서 source로 전류가 흐르고

P 형이면 -걸때 Source 에서 drain 으로 전류가 흐르고.....

'Learning stuff' 카테고리의 다른 글

| mearly machine diagram (0) | 2012.12.11 |

|---|---|

| page mapping (0) | 2012.12.04 |

| 엑셀로 피팅 (0) | 2012.08.08 |

| SBD (0) | 2012.08.03 |

| 오프컬렉터 (0) | 2012.08.03 |

설정

트랙백

댓글

글

엑셀로 피팅

'Learning stuff' 카테고리의 다른 글

| page mapping (0) | 2012.12.04 |

|---|---|

| mosfet 기호 (0) | 2012.09.11 |

| SBD (0) | 2012.08.03 |

| 오프컬렉터 (0) | 2012.08.03 |

| labview (0) | 2012.07.27 |

설정

트랙백

댓글

글

SBD

SBD에는 일반 다이오드와는 크게 다른 점이 있습니다. 일반적인 다이오드는 P형과 N형 반도체의 접합(PN접합)으로 되어 있습니다만, SBD는 금속과 반도체의 접합으로 되어 있습니다.

특성적으로는 PN접합과 유사한 정류 특성을 나타냅니다만, 내부를 들여다보면 큰 차이가 있습니다. PN 접합의 다이오드는 다수 캐리어와 소수캐리어에 의해 전하가 옮겨집니다만, SBD는 다수캐리어 밖에 없습니다. 이 때문에 매우 고속의 동작이 가능한 관계로, 고주파 영역에서 사용하기 좋다고들 하지요.

SBD의 눈에 띄이는 또한가지 특성 중 하나는, 역방향 전압과 순방향 전압이 낮다는 것입니다. 역방향 전압은 일반 PN 접합 다이오드보다 1자리수 정도 낮고, 순방향 전압은 상대적으로 반정도밖에 되지 않습니다.

<그림 9-1>에 고주파에서의 SBD 등가회로를 나타내었습니다. 직렬저항 Rs, 비선형 접합저항 Rj, 비선형 접합 캐패시턴스 Cj로 구성되어 있습니다. SBD를 검파회로와 믹서에 사용할 때는 Rs와 Cj가 작은게 좋습니다.

<그림 9-1> 쇼트키 배리어 다이오드 (SBD) 등가회로

'Learning stuff' 카테고리의 다른 글

| mosfet 기호 (0) | 2012.09.11 |

|---|---|

| 엑셀로 피팅 (0) | 2012.08.08 |

| 오프컬렉터 (0) | 2012.08.03 |

| labview (0) | 2012.07.27 |

| matlab interp (2) | 2012.07.27 |

설정

트랙백

댓글

글

오프컬렉터

오픈 컬렉터(open collector) 출력의 장단점

저번시간에 이어 오픈컬렉터에 대해 알아보겠습니다.

먼저 오픈컬렉터는 트랜지스터의 컬렉터가 오픈된 채로 출력 핀으로 나와 있기 때문에

오픈 컬렉터 출력이라고 했는데요 그럼 오픈컬렉터를 사용하는 이유는 무엇일까요?

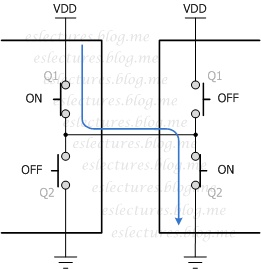

토템폴 출력에서 출력단을 구성하는 두 스위치가 동시에 ON 상태에 있어서는 안됩니다.

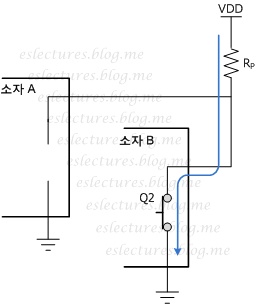

아래 그림을 예로 보자면

왼쪽 소자의 논리 ‘1’ 출력과 오른쪽 소자는 논리 ‘0’ 출력을 서로 연결하면 왼쪽 소자의 VDD에서

오른쪽 소자의 GND까지 전류가 흐르게 됩니다.

결과적으로 과전류가 흐르기 때문에 이런 상태가 지속되면 소자가 파괴되겠죠.

오픈컬렉터의 경우 소자 A의 Q2가 [OFF] 소자 B의 Q2가 [ON] 상태로 두 출력을 서로 연결하여도

오픈 컬렉터 소자는 회로에서 분리된 상태로 회로의 다른 부분에 아무런 영향을 미치지 않게 됩니다.

요약하자면 오픈 컬렉터 출력을 서로 묶으면 개별 소자의 출력 중 단 하나라도 논리 ‘0’을 출력하면

전체 출력은 논리 ‘0’이 되고 개별 소자의 출력이 모두 논리 ‘1’일 때에만 전체 출력이 ‘1’이 됩니다.

이것은 각 개별 소자의 출력을 AND 게이트로 연결한 것과 논리적으로 같은 결과이므로

이렇게 오픈 드레인 출력을 모두 묶은 구조를 선으로 연결한 AND라는 뜻으로

와이어드 AND (wired AND) 연결이라고 부르죠.

오픈컬렉터의 장점

1.확장성이 뛰어난 와이어드 AND 연결이다.

2.소자의 동작 전원 전압과 다른 전압을 출력할 수 있다.

단점

1.토템폴 소자에 비해 속도가 느리다.

2.풀업 저항으로 인해 전력 소비가 발생한다.

'Learning stuff' 카테고리의 다른 글

| 엑셀로 피팅 (0) | 2012.08.08 |

|---|---|

| SBD (0) | 2012.08.03 |

| labview (0) | 2012.07.27 |

| matlab interp (2) | 2012.07.27 |

| Converters (0) | 2012.04.12 |

설정

트랙백

댓글

글

labview

다까먹음 ㅋㅋ 그게 중요함 ㅋㅋ

여튼 뭐 많이 캡쳐해났는데 설명하기는 귀찮고 그냥 파씽해야지

에라이 잘 보이지도 않네 ㅋㅋ

이것들은 한번 시험삼아서 내가 생각하고 있는 이 컨셉이 맞나 싶어서 만들어 본 것 들이다.

참고로 프로그램이 커지면 랩뷰는 불편하다 아주 ㅠ 선이많아서....

여튼 글로 쫌 적어나야지

1. while loop 의 원리는 똑같다. 근데 특이한 점이 while 문에 equal 5 할때 끝나게 해놓으면 5일때도 실행하고 끝난다 즉 while(x!=5)했는데 5일때도 실행하고 끝난다. while 보다는 while do 같다. 실행하고 조건검사 하는듯. 그리고 while 문 안에 읽고 싶은 값이 있어야 계속 scan이 가능하다. 무슨말인지 모르겠지만 아주 당연한 소리이다. 예를 들어 내가 죽어라 썼던 PLZ334WL에서 Voltage 값을 읽어오고 싶다( 물론 active load 지만...) 여튼 이러면 while 문 안에 그게 있어야지 계속 값을 스캔 해 온다. 그리고 while 문이 끝나야 그 값이 밖으로 뿅 나간다. 이것도 무슨 소리인지 모르겠지?? 예를들어 PLZ334WL 에서 Voltage 값을 읽어오는 선이 중간에 while 문 루프를 지나가고 indicator 로 간다고 치자.. 그러면 while 문이 끝날때 까지는 읽어온 그 값은 indicator 에 가지 않는다. 즉, while(); 효과가 난다는 말이다.

2. case를 써서 step을 만들것(case의 1,2,3,4 를 조건에 따라 변경시키고 그 조건은 또한 조건(if==case)을 써서 변화 시킴)

가장 기본적인 구조 같은데 while 문을 집어넣고 그 만에 case 문을 넣어서 step을 변경해 가면서 실행한다. 그리고 while 문에 shift register를 추가시키고 1을 증가시키면서 어떠한 조건이 되면 while 문이 끝나게 한다. 그리고 필요하다면 flat sequence 구조도 적절하게 잘 사용해 주면 좋다! 사실 이게 다다...ㅋㅋㅋ

3. while 문이 두개가 있다고 가정하고 안에의 while문이 계속 돌고있다고 가정할때 두개의 while 문 밖에서 값을 변화 시켜도 그 변경된 값이 안에서는 update 되지 않는다.

4. 모든 while 문은 parallel 하게 돌아간다.

5. 파일 저장에서 path 가 바뀌게 되면 바로 그파일 write 를 중지하고 변경된 path 에 맞는 장소에 저장을 시작한다.

6. 여러 디바이스를 한꺼번에 많이 실행하면 timeout error 가 난다. 그러니까 flat sequence를 써서 따로따로 실행하게 단계를 나누어주셈.

7. 랩뷰는 멍청하다

8. end of line 이 아니라 carriage return constant 가 엔터다.

9. close vi 를 따로 만들어서 session close 를 처리 해 준다. 이건 어떻게 이벤트 처리를 하면 될것 같기도 한데.... 몰라 ㅋㅋ

10. 배열(array)의 행과 열은 0부터 시작한다.

마지막으로 finally 만든 vi

한장에 안담기니까 일부분만 김치

'Learning stuff' 카테고리의 다른 글

| SBD (0) | 2012.08.03 |

|---|---|

| 오프컬렉터 (0) | 2012.08.03 |

| matlab interp (2) | 2012.07.27 |

| Converters (0) | 2012.04.12 |

| OP AMP의 기본동작 (1) | 2012.04.11 |

설정

트랙백

댓글

글

matlab interp

요즘은 그래도 쫌 널널하니까 야아깐

최근 가장많이 한게 labview 와 matlab 이다.

가장 헷깔리는걸 기록하자면

matlab에서 좌표는

요거란 거다

meshgrid를 쓰면 저거의 반대지만

이경우를 제외한 나머지는 저런듯.....

그래서 [y,x,z]=meshgrid(y,x,z) 이렇게 적거나

귀찮으면 [x,y,z]=ndgrid(x,y,z) 이렇게 하여 mesh form의 grid를 형성해 준다.

난 주로 curve fitting 의 용도로 interp3, inter2, inter1 을 사용하였는데

이상한 오류가 나는 바람에 딴걸 알아보다 보니까.. 응 더 좋은걸 오늘 알게 되었다.

그 두개가 triscatteredinterp 와 griddata 다 griddata 얘는 griddata3로 하면 3D도 되네?? 근데 뭐 어쩄든 얘들 좋은점이 Non uniformly spaced sample들로 fitting 할수 있다는거

근데 griddata 얘는 쓰기 싫은게 linear 하고 nearest 밖에 안되여.... triscatteredinterp 는 fitting 된 function을 생성해주고 얘는 보니까 column vector 형태로 in 을 넣어죠야 되더라..... 자세한건 검색요........

Create a data set:

x = rand(100,1)*4-2; y = rand(100,1)*4-2; z = x.*exp(-x.^2-y.^2);

Construct the interpolant:

F = TriScatteredInterp(x,y,z);

Evaluate the interpolant at the locations (qx, qy). The corresponding value at these locations is qz .

ti = -2:.25:2; [qx,qy] = meshgrid(ti,ti); qz = F(qx,qy); mesh(qx,qy,qz);

Data gridding and hypersurface fitting for 3-D data

Syntax

Description

w = griddata3(x, y, z, v, xi, yi, zi) fits a hypersurface of the form  to the data in the (usually) nonuniformly spaced vectors (

to the data in the (usually) nonuniformly spaced vectors (x, y, z, v). griddata3 interpolates this hypersurface at the points specified by (xi,yi,zi) to produce w. w is the same size as xi, yi, and zi.

Examples

Example 1

Interpolate the peaks function over a finer grid.

[X,Y] = meshgrid(-3:.25:3); Z = peaks(X,Y); [XI,YI] = meshgrid(-3:.125:3); ZI = interp2(X,Y,Z,XI,YI); mesh(X,Y,Z), hold, mesh(XI,YI,ZI+15)

Examples

To generate a coarse approximation of flow and interpolate over a finer mesh:

[x,y,z,v] = flow(10); [xi,yi,zi] = meshgrid(.1:.25:10, -3:.25:3, -3:.25:3); vi = interp3(x,y,z,v,xi,yi,zi); % vi is 25-by-40-by-25slice(xi,yi,zi,vi,[6 9.5],2,[-2 .2]), shading flat

참고로... extrapolation은 spline 밖에 안되더라 그래

마지막으로 몇개의 데이터로 3D Interpolation 한 결과 ㅋㅋ

나중에 보면 기억날진 모르지만 스토리는 대략

1. Vin 별 데이터를 받아서 downsample 을 Vout 방향으로 0.5 간격으로 해주어서 자료를 줄인후에 나온 자료들 가지고 interp3 하거나

2. 저 위에껀 있는 그래프의 결과인... 그래 일단 측정한 자료의 값들을 column vector로 쫙 뽑아내서 triscatteredinterp 를 통과시켜주어서 함수를 뽑아낸 다음 그린다!

간단하네 뭐.. ㅋㅋ

'Learning stuff' 카테고리의 다른 글

| 오프컬렉터 (0) | 2012.08.03 |

|---|---|

| labview (0) | 2012.07.27 |

| Converters (0) | 2012.04.12 |

| OP AMP의 기본동작 (1) | 2012.04.11 |

| Open collector, Open drain (0) | 2012.04.11 |

설정

트랙백

댓글

글

Converters

우리가 회로를 꾸밀 때 있어서 전원이란 것은 정말 중요하지요.

"근본이 제대로 되어 있어야 한다"

라는 말처럼 전원 자체에 문제가 있다면 아무리 좋은 회로라 해도 단순 멍텅구리일 뿐입니다.

그런 의미에서 우리가 정말 회로에서 자주 사용하는 Regulator(레귤레이터)라는 놈에 대해 한번은

짚고 가야 할 듯합니다.

일반적으로 Linear Regulator, LDO, Step-Down, Step-up, Boost-Buck Converter가 많이 사용되고 있지요..

각각의 구조와 특징에 대해서 잠깐 살펴보도록 하지요~

1) Linear Regulator

우리가 보통 리니어 레귤레이터라고 하면 78XX시리즈가 대표적이라 할 수 있겠습니다.

뭐 회로에 대해 조금이라도 접해본 사람이라면 정말 많이 보았을 소자입니다.

78XX에서 뒤의 XX의 숫자가 보통 Output Voltage를 말하는데요..

예를 들어 7805라면 5V가 정전압으로 출력되겠구요.. 7806이면 6V, 7812라면 12V가 정전압으로 출력되어 나옵니다.

사실 정전압을 얻기 위해 회로가 간단하고 고주파 Switching을 하는 방식이 아니기 때문에 안정된 전원을 공급해주지요.

하지만 효율이 떨어진다는 큰 단점이 있지요. 효율이라고 하면 입력된 에너지보다 출력되는 에너지의 %비율입니다.

또한 주의 할것이 있는데 Linear Regulator는 출력전압보다 입력전압이 약 2~3V는 더 높게 주어야 합니다.

그 이유는 아래 그림을 통해 차차 알아보아요~

리니어 레귤레이터는 위와 같은 구조로 되어있습니다. 물론 내부가 모두 저렇다고 하는게 아니라 원리가 그렇다는 거에요~

위의 그림에서는 TR을 그려놨지만 그 바로 위의 그림처럼 사실은 등가적으로 가변저항이 되는 것이죠.

출력되는 전압을 비교기의 Non-Inverting에 넣고 기준이 되는 Reference 전압과 비교(사실 이게 원하는 출력전압이 되겠죠)하여 기준전압보다 높으면 Base 신호에 Low를 주어 입력신호를 차단해주고, 반대로 기준전압보다 낮으면 Base를 High호 해서 입력전원을 부하에 공급해 주게 되는 원리지요.

여기서 중요한 것은 등가적으로 보았을 때 가변저항이라고 했으니까 사실은 저항성분을 통해 높은 입력 전압을 강압해주는 것을 통해 일정한 출력전원을 공급해주는 것이죠.

즉, 9V를 입력해주고 출력을 5V를 얻었다면 4V가 강압된 것이고, 그 4V의 전압강하는 Regulator의 내부에 걸리게 되는 것

입니다.

그렇기 때문에 리니어 레귤레이터를 사용하여 높은 전류를 흘려주게 되면 굉장히 뜨겁게 되는 거에요~

만약 9V입력에 500mA의 전류를 공급하고 출력이 5V였다면, 4V의 전압강하에 500mA의 전류가 흘렀으니까

P = V*I = 4 * 500mA = 2000mW = 2W

의 전력이 레귤레이터에서 소비가 되는 거에요~ 이 소비되는 전력은 모두 열에너지로 방출되기 때문에 그만큼 레귤레이터의 온도가 올라가 뜨거워 지는 원리입니다.

따라서 방열판과 같은 것을 꼭 부착해 주어야 합니다요~

또한 이렇게 레귤레이터의 내부에서 소비되는 에너지가 있기 때문에 아까 위에서 입력전압을 출력전압보다 반드시 2~3V높게 걸어주라고 했던 것입니다. 만약 출력전압과 같거나 더 낮게 된다면 처음에는 좀 견디는듯 하다가 끝내 소자가 나가버립니다.

다음으로 위의 그림에서 입력과 출력쪽에 각각 캐패시터가 있는데 이것은 일종의 LPF(Low Pass Filter)로 전원 성분에 있는 고주파 성분을 끌어당겨 GND로 보내버리게 되지요. 즉, 저주파인 DC 성분만 공급되도록 하는 역할이에요~

뭐 사실 레귤레이터의 데이터시트를 보시면 캐패시터의 값이 나와있으니 참고하시면 되겠습니다.

참고로 LDO(Low Drop Out)이라는 레귤레이터가 따로 있는데 이는 말그대로 입력전압에 비해 출력전압의 전압강하가 작을 때 사용하는 레귤레이터 입니다. 우리가 잘 사용하는 소자로 LM1117과 같은 소자가 있는데 5V -> 3.3V 정도로 낮은 전압강하를 사용할때는 LDO를 사용하는 것이 훨씬 좋습니다. 왜냐하면 그만큼 발열되어 날라가는 에너지가 적기 때문에 방열판을 달아줄 걱정이 없고, 소자의 크기도 작게 나와 크기를 줄일 수 있는 장점이 있기 때문이지요~

다만 그만큼 흘려줄수 있는 전류의 양이 적기 때문에(보통 1A이하) 저전력소자를 구동할 때 자주 사용됩니다.

2) Step-Down(Buck) Converter

다음으로 볼것이 바로 일명 Step-Down 또는 Buck Convertor라 불리는 놈이 되겠습니다.

Buck이라는 말은 "날뛰다, 걷잡을 수 없이 흔들리다"라는 뜻이 있더군요.(사실 저도 첨 알았음 ㅎㅎ;;)

Step-Down이라는 말도 "단계적으로 내리다" 라는 뜻이겠네요.

일단 원리를 알기 전에 알아두어야 할 중요한 이론이 하나 있는데요. 바로 PWM(Pulse Width Modulation)이라는 것입니다.

말 그대로 펄스 폭 변조라는 말인데요.

이런 PWM 파형을 이용하여 전압을 낮추는 결과를 얻어내는 것이지요.

아래 그림을 한번 보시죠~

위의 그림과 같이 펄스에서 On time 즉, High 구간의 폭이 한 주기 시간동안 얼마나 되느냐에 따라 Duty rate가 결정

되겠습니다. 상식적으로 생각할 때 우리가 모터에 위와 같은 파형을 주게 된다면 High 구간에서는 모터의 출력이 최대

가 되어 최고 속력으로 돌고 Low 구간에서는 전원이 끊긴것이니까 멈춰야 하겠죠?

하지만 실제로는 그렇지 않다는 것이죠. 한주기의 시간이 엄청나게 긴 시간이 아니라면 실제적으로 걸리는 전류값는

위와 같이 Duty rate만큼 평균적으로 걸린다고 생각하시면 됩니다. 즉, 본래 최대 100의 출력이 걸릴 수 있을 때

Duty rate가 5%라면 5만큼의 출력이 지속적으로 걸리고 있다는 것이고, Duty rate가 50%라면 50의 출력이 지속적

으로 걸리게 된다는 것이죠~

음.. 그렇다면 입력전원으로 최대 전압이 12V이면서 이 전원을 PWM 형식으로 걸어주면 출력은 Duty Rate에 따라서

입력보다 작은 전압이 출력되겠네요~

아항! 이것이 바로 Buck 또는 Step-down Convertor의 원리입니다.

위의 그림이 바로 Step-down convertor의 회로입니다.

일단 동작 원리를 순차적으로 한번 볼까요?

① 전원 전압 Vi가 N-MOSFET의 Drain으로 인가됩니다. 여기서 MOSFET가 사용되는 이유는 빠른 스위칭에 적합하기

때문이에요~ 어떤 MOSFET를 사용하는가에 따라 성능이 달라지겠죠~

② Gate에 걸린 PWM 파형이 High 구간이라면 MOSFET은 On-state가 되어 Drain에서 Source로 전류가 흘러들어갑니다.

③ Source를 통해 인가된 전원은 사실 굉장히 짧은 시간의 Gate에 걸린 High 신호로 들어온 전원신호이기 때문에 실제적

으로 엄청 고주파적인 신호가 됩니다. 이런 고주파성 신호를 L과 C로 구성된 LPF(Low Pass Filter)를 통하게 하여 고주 파성분을 제거하고 부하에 걸려 출력전압 Vo가 출력되게 되지요.

④ L과 C가 On-Time동안 완충상태가 되면(아시겠지만 L과 C는 에너지를 저장할 수 있는 소자입니다!) 이제 MOSFET의 Gate신호에 Low 신호를 주어 입력전원을 차단시켜 Off-State가 되게 합니다. 이렇게 되면 인덕터에 저장되었던 에너지가 방전을 시작하고, 순간적이지만 마치 입력전원처럼 작용하여 계속적으로 부하에 전원을 공급해주게 됩니다.

⑤ 이 때 MOSFET를 제외하고 Close-Loop를 생성하기 위해서 중간에 위의 그림과 같이 다이오드가 들어가게 되는 것이죠.

이렇게 인덕터의 에너지가 모두 방출되어 전압이 어느정도 떨어지면 FeedBack을 통해 감지하고 다시 Gate를 High상태로 만들어 On-State가 되고 전원을 공급해주게 되는 원리입니다.

이와 같이 MOSFET의 Gate단에 PWM 신호를 주어 입력전압보다 출력전압을 낮게 만들 수 있는 것이지요.

따라서 출력전압과 입력전압에 대해 아래와 같은 식을 유도할 수 있습니다.

Vo = D * Vi

>> D = Duty-rate, 시비율 혹은 통류율

즉, 시비율 D는 0 < D < 1 의 값을 가지게 되지요. 쉽게 말하면 Gate에 걸리는 PWM 파형의 On-State Time에 따라 변한다는 거죠~

3) Step-Up(Boost) Converter

Boost Convertor는 위에 설명했던 Buck Converter와는 반대로 승압을 해주는 기능을 해줍니다.

근데 사실 알아두어야 할 것이 있는데요.. 실제 공급해주는 에너지는 같은 것이니까 승압을 하던지 강압을 하던지 출력되는 에너지

는 이상적으로 같다는 것을 알아두셔야 합니다.

다시말하면 에너지 적으로 P=V*I 인데.. V값을 낮추면 I값은 높아지는 것이고, V값을 높이면 I값는 감소한다는 거에요.

따라서 Boost convertor를 사용한다면 그만큼 공급되는 전류값는 작아진다는 의미입니다.

예를 들어 5V, 1A를 공급해 주었는데 12V, 1A로 공급해줄 수는 없다는 거에요~ 5*1 = 5W니까.. 12 * 0.416 = 5W가 된다는 것이

지요.. 즉, 1A에서 400mA로 공급되는 전류값은 낮아진다는 의미입니다. 그것을 꼭 염두해 주셔야 해욧!

다시 설명으로 들어가자면.. 원리는 Buck 컨버터와 비슷하고.. 모양도 은근히 비슷하네요..

MOSFET와 L, Diode의 위치가 각각 변경되었군요..

동작원리를 살펴보면요..

① On-State 동안 인턱터 L이 충전이 되겠구요..② L의 충전이 완충이 되면 Off State로 들어가게 되고 이 때 본래의 입력전압 Vi와 인덕터에서 방전되는 VL이 더해져서

부하와 캐패시터에 전원을 공급하게 되겠네요~ 전류의 방향은 위의 그림과 같구요~ 폐회로를 위해서 MOSFET의 다이오드를 통해 전류가 흐르고 있음을 주의하시길 바래요~

③ 이렇게 Off-State에서 본래의 전원과 인덕터에서 충전된 에너지가 같이 공급되기 때문에 실제 공급되는 전압은

Vi + VL이 되어 본래 전압보다 VL의 전압이 더 승압되어서 부하에 공급되기 때문에 승압이 되는 것입니다.

4) Boost-Buck Converter

Boost-buck converter는 Boost와 Buck의 회로모양을 조금씩 따라하여 승압과 강압을 시비율 D에 따라서 결정해 줄 수 있는 회로입니다. 즉, 시비율이 0.5보다 크게 되면 승압이 되고, 0.5보다 작으면 강압이 되는 뭐 그런 원리이지요~

동작원리는 Boost와 비슷하게 인덕터L가 On-state동안 충전되다가, Off-state가 되면 다이오드의 방향에 따라 인덕터가 방전되면서 역방향 전류가 부하와 캐패시터에 흐르게 되어있습니다.

다시 한번 말씀드리지만 전원의 극성이 Negative로 바뀐다는 것을 꼭 염두해주시길 바랍니다~

'Learning stuff' 카테고리의 다른 글

| labview (0) | 2012.07.27 |

|---|---|

| matlab interp (2) | 2012.07.27 |

| OP AMP의 기본동작 (1) | 2012.04.11 |

| Open collector, Open drain (0) | 2012.04.11 |

| schmitt trigger (0) | 2012.04.11 |

설정

트랙백

댓글

글

OP AMP의 기본동작

봐도봐도 맨날 헤깔리는 OP AMP

뭐.... 일단 난 디테일한 부분보다는 일종의 인터페이스만 알면 되니까 ㅋㅋㅋ

OP AMP 를 해석할때 생각 하기 쉬운 방법이 있습니다. 기본적인 건 OP AMP 가 무한대의 저항의 가지는것에 있지만... 맞나?? 여튼

포인트는 두 입력 단자는 동 전위이다 에서 시작 합니다. 다시 말해 "두 입력 - , + 이 같은 전압이 되려는 쪽으로 출력은 동작한다" 가 된다. 이걸 가상 쇼트라고 그러는데 그 이유는 마치 내부적으로 두 입력단자가 쇼트된것처럼 동작하기 때문입니다.

예를 들어 이걸보자

위 회로를 보면 + 단자가 그라운드에 연결 되어 있다. 즉 (-)단자도 0V가 되는 방향으로 변한다는거

Vi 가 0보다 커지면 (-)단자가 0이 되기 위해서는 출력은 (-)신호가 되어야한다. 그렇기 때문에 출력은 (-) 이 되고 그때 D1 으로 전류가 흐르고 D2로는 역방향으로 흘러야 하기 때문에 off 가 되는 것이라.

Vi 가 0보다 작아져도 똑같습니다. 출력이 + 신호를 보내야 하기 때문에 D2 는 순방향이 되므로 전류가 흐로고 D2는 역방향이므로 전류가 흐르지 않아요

끝!

'Learning stuff' 카테고리의 다른 글

| matlab interp (2) | 2012.07.27 |

|---|---|

| Converters (0) | 2012.04.12 |

| Open collector, Open drain (0) | 2012.04.11 |

| schmitt trigger (0) | 2012.04.11 |

| Monostable (0) | 2012.03.24 |

설정

트랙백

댓글

글

Open collector, Open drain

이를 이해하기 위해서는 먼저 아래의 [기초 강의]에서 설명한 TTL 및 CMOS의 기본 원리나 [집중 분석]에서 설명한 토템폴(totem-pole) 방식을 이해하여야 한다.

일반적인 TTL 소자는 출력간의 회로가 토템폴 방식으로 되어 있어서 출력단을 구성하는 2개의 트랜지스터중에서 항상 1개가 ON 상태를 유지한다. 즉, 출력이 "H" 상태인 경우에는 상위 트랜지스터가 ON되어 출력전류가 안에서 밖으로 흘러나오는(source current) 동작을 수행하고, 출력이 "L" 상태인 경우에는 하위 트랜지스터가 ON되어 출력전류가 밖에서 안으로 흘러들어가는 (sink current) 동작을 수행한다.

CMOS 소자의 경우에도 트랜지스터가 바이폴라 트랜지스터 대신에 FET로 바뀌고 출력단 회로가 약간 다른 것을 제외하면 기본적으로는 이와 같은 동작을 한다. 즉, CMOS의 경우에는 TTL에서처럼 출력단 회로에서 저항이나 다이오드가 없이 단순히 상위 및 하위에 1개씩의 FET로만 구성된다. 이 CMOS의 경우에도 상위 및 하위 트랜지스터는 반드시 1개만 ON되는데, CMOS(Complementary MOS)라는 말은 바로 이를 가리킨다. 즉, 2개의 트랜지스터중에서 1개가 ON되면 반대로 나머지 1개는 반드시 OFF되는 출력단 구조를 상보형(complementary) 구조라고 부르는 것이다.

이러한 개방 콜렉터나 개방 드레인형의 디지털 소자를 사용할 때는 잘못하면 회로가 정상적으로 동작하지 않는 것은 물론이고 소자가 소손되어 망가질 수 있으므로 매우 주의해야 한다.

위의 <그림 1>에서 처럼 1개의 디지털 소자 출력이 여러개의 부하를 구동하는 것은 팬아웃만 초과하지 않으면 아무 문제가 없다. 팬아웃은 쉽게 말하면 부하를 구동할 수 있는 전류 용량이며, 이 용량의 범위내에서는 올바른 디지털 출력전압 레벨을 보장할 수 있게 된다.

그러나, <그림 2>의 경우처럼 여러개의 출력을 묶어서 1개의 부하에 연결할 필요성이 있을 때는 함부로 이렇게 하면 안된다. 그 이유는 출력단 회로의 동작원리를 생각하면 쉽게 알 수 있다. 즉, <그림 3>을 보라. TTL 소자의 경우에는 <그림 3>의 왼쪽에 해당하는데, 이때에도 1개로 묶여져 있는 모든 소자의 출력단이 항상 모두 "H" 상태나 "L" 상태를 유지한다면 별 문제가 없다. 그러나, 일반적으로 이 출력단에는 "H" 상태를 가지는 것과 "L" 상태를 가지는 것이 공존하게 될 것이다. 그렇게 되면 이들 출력단이 선으로 직접 접속되어 있으므로 곧바로 단락회로가 되어 "H" 출력단에서 흘러나온 큰 단락전류가 전류가 "L" 출력단으로 흘러들어가게 된다. 이러한 상황이 오래 방치되면 출력단의 트랜지스터들을 파괴시킬 수도 있을 것이다. 물론 토템폴의 출력단에는 윗쪽 트랜지스터의 콜렉터측에 직렬저항이 있지만 이는 수십Ω 이하의 매우 작은 값이므로 사태를 해결할 수 있는 정도가 되지 못한다.

이러한 최악의 상황은 <그림 3>의 오른쪽과 같은 CMOS에서도 마찬가지로 발생할 수 있다. CMOS의 경우에는 그나마의 직렬저항도 없으므로 더욱 큰 단락전류가 흐르게 될 것이다.

그러면 이러한 사태를 방지하려면 어떻게 해야 하는가? 그것은 2가지로 설명할 수 있다.

첫째로, 일반적인 디지털 소자는 출력을 이와 같이 직접 접속하면 안된다. 논리적으로는 출력을 이렇게 묶으면 이는 부논리로 OR의 기능을 수행하므로 배선논리 OR(wired-OR)라고 하는데, 이를 사용하려면 그에 합당한 조건이 필요하다.

둘째로, 꼭 이러한 wired-OR 회로를 사용해야 한다면 출력단이 전원단락을 일으키지 않는 구조를 가지는 디지털 회로를 사용하는 것인데, 이러한 출력단 회로에는 개방 콜렉터/개방 드레인형의 방식과 3상태(3-state) 방식이 있다.

TTL에서 개방 콜렉터 방식으로 사용한 예를 <그림 4>의 왼쪽에 보였다. 그림에서 보듯이 개방 콜렉터 구조에서는 위쪽의 트랜지스터가 없고, 아래쪽 트랜지스터의 콜렉터가 그대로 밖으로 개방되어 출력되는 구조를 가진다. 따라서 여러개의 출력을 직접 접속하더라도 단락의 위험이 없어지게 된다. 여러개의 출력중에서 단 1개라도 "L" 상태이면 다음단의 입력은 "L"로 결정된다.(부논리로 OR) 그러나, 이들 출력이 모두 "H" 상태라면 이는 실제로 "H"가 되지 못하므로 다음단의 입력은 "H"나 "L"로 되지 못하고 부동상태(floating state)에 있게된다. 따라서, 이러한 바람직하지 않은 결과를 방지하려면 개방 콜렉터형의 wired-OR 회로에서는 반드시 이 묶여진 출력단을 수KΩ 정도의 저항으로 +5V 전원에 풀업(pull-up)시켜 주어야 한다.

CMOS에서는 똑같은 상황을 개방 드레인이라고 부르며, 역시 이에 관한 회로를 보이면 <그림 4>의 오른쪽과 같다.

이러한 개방 콜렉터나 개방 드레인 회로가 사용되는 전형적인 예는 여러개의 주변장치가 CPU에게 인터럽트를 요구하는 인터럽트 신호선이다. 대부분의 마이크로프로세서에서 인터럽트 신호선은 low active로 되어 있으며, 이 경우에는 개방 콜렉터나 개방 드레인 회로가 그대로 적용될 수 있는 것이다.

한편, 이처럼 출력단을 1개로 묶어 사용하는 것은 3상태 회로를 사용하여 구성할 수도 있다. 그러나, 이 경우에는 모든 출력단을 하이 임피던스 상태(Z)로 disable시켜 놓았다가 필요할 때마다 다음 단의 입력으로 연결하고자 하는 출력단 1개만을 enable시키는 방법으로 제어해야만 한다. 이러한 예는 마이크로프로세서 시스템에서 모든 칩선택 신호들이 주변장치들중에서 오직 1개만을 데이터 버스에 선택적으로 접속하는 동작이 이에 해당하며, RS-485 통신에서의 수신부 회로에서도 이러한 구조가 적용됨을 찾아볼 수 있다.

이상에서 보았듯이 개방 콜렉터/개방 드레인 구조나 3상태 구조를 가지는 소자는 일반 상보형 동작을 수행하는 디지털 소자와 매우 다르게 사용된다. 따라서, TTL이나 CMOS 소자들에서는 이러한 특이 출력형의 소자들을 나머지의 일반 소자들과 엄격히 구분하여 표시하고 있다. 예를 들면 6개의 인버터를 포함하는 7404는 "Hex Inverter"라고 부르지만, 이것의 개방 콜렉터형인 7405는 "Hex Inverter with Open-Collector Outputs"라고 부른다.

[출처] 오픈 콜렉터와 오픈 드레인 방식이란 무엇인가|작성자 라이더

'Learning stuff' 카테고리의 다른 글

| Converters (0) | 2012.04.12 |

|---|---|

| OP AMP의 기본동작 (1) | 2012.04.11 |

| schmitt trigger (0) | 2012.04.11 |

| Monostable (0) | 2012.03.24 |

| 낸드으 플래시_1 (0) | 2012.03.13 |

설정

트랙백

댓글

글

schmitt trigger

[ Schmitt Trigger ]

Schmitt Trigger는 미국의 과학자 Otto H. Schmitt에 의해 발명된 일종의 비교기로써, 하나의 입력 전압과 출력 전압, 두 개의 threshold를 가진다. negative feedback을 사용하는 비교기로, OP Amp의 구조를 가지며 대부분 inverter로 사용된다.

< Schmitt Trigger 회로 >

즉, input 신호로 low threshold 보다 낮은 전압이 인가되면 출력은 high로, high threshold 보다 높은 전압이 인가되면 출력은 low가 되며, 두 개의 threshold 사이의 전압이 인가되면 그 값을 유지한다.

threshold가 하나인 유사한 시스템의 경우, 입력 신호에 noise가 섞여 threshold에 비슷한 전압이 인가되면 스위치를 순식간에 on/off 시킬 수 있기 때문에 두 개의 threshold를 사용하는 Schmitt Trigger가 더 안정적이다. 그러므로 사람의 손 떨림으로 인해 값이 여러번 입력되는 등의 switch noise를 제거할 수 있다.

슈미트 트리거 [ Schmitt triger ]

히스테리시스 특성을 갖도록 한 비교기. 비교기는 하나의 전압을 다른 기준 전압과 비교하기 위한 것인데, 비교기의 입력 측에 나타나는 잡음 전압은 출력 측에 오차를 유발하기 때문에 비교기가 잡음에 둔감하게 작용하도록 히스테리시스 정궤환법을 사용한다. 히스테리시스는 입력 전압이 높은 값에서 낮은 값으로 갈 때보다 낮은 값에서 높은 값으로 갈 때 높은 레벨이 되므로, 2개의 트리거 레벨이 절체 동작에서 오프셋 또는 지연되는 특성을 이용하여 입력에 포함된 약간의 잡음은 출력에 영향을 미치지 못하도록 한 것이다.

쉽게 말로 설명하자면 High 와 Low상태의 전압이 0v와 5v의 접압차이를 보일때 입력돼는 신호는 깨끗하게 0v와 5v로 들어오는 것이 아니라 아날로그 신호와 같이 2.3v나 4v식으로 입력이 들어올 수 있다 이때 슈미트 트리거를 이용해서 기준접압을 2.5v이상은 High로 이하는 Low로 정하는 등의 방식이 가능한 하나의 비교기이다

히스테리시스 [ hysteresis ]

과거의 경력에 따라 물리적 양이 변화하는 현상. 특히 자기 히스테리시스를 단지 히스테리시스라고 할 때도 있다. 재료가 환경의 조건에 따라서 성질이 바뀌는데, 그 재료에 의해서 나타나는 현상. IC에서는 정궤환을 건 회로에서 입력 전압변화에 관계되는 출력이 되는 상태로서 입력 특성이 불감이 되는 폭을 말한다. 이력현상이라고도 한다.

'Learning stuff' 카테고리의 다른 글

| OP AMP의 기본동작 (1) | 2012.04.11 |

|---|---|

| Open collector, Open drain (0) | 2012.04.11 |

| Monostable (0) | 2012.03.24 |

| 낸드으 플래시_1 (0) | 2012.03.13 |

| SDK axi_timer_ds764 (0) | 2012.03.05 |